实验一、组合逻辑电路设计

上一节

下一节

实验一、组合逻辑电路设计

扩展内容:基于ModelSim仿真步骤

1、在D盘以姓名的拼音新建文件夹,如ZhanSan

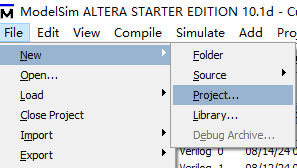

2、在ModelSim下,点击File->New->Project,新建项目

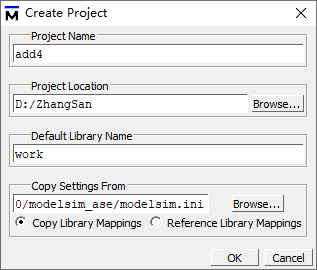

3、将项目保存到D盘的ZhangSan文件夹中,项目名为add4

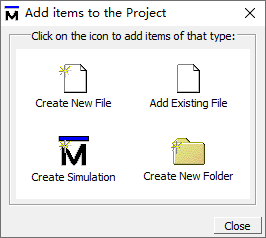

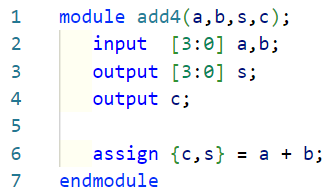

4、如果文件不存在,则选择新建文件,如果文件存在,则可以导入

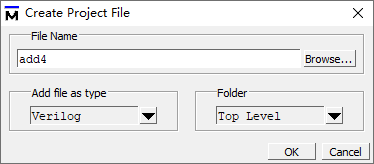

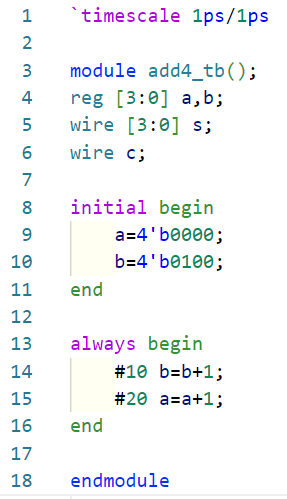

5、此处以新建文件为例,新建文件add4,选择文件类型为Verilog

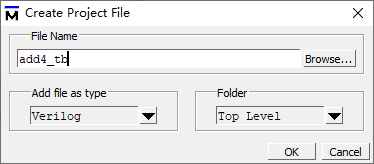

6、再次新建一个文件,名为add4_tb

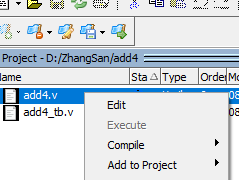

7、右击add4选择Edit编辑

8、录入add4代码,保存

9、录入add4_tb代码,保存

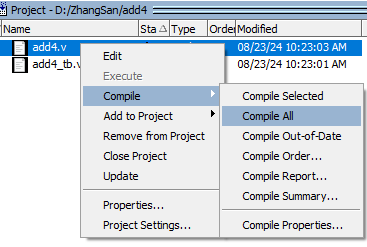

10、编译所有文件

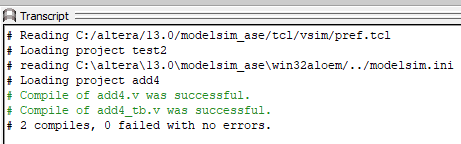

11、查看编译结果,无错误

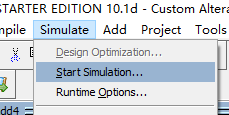

12、点击Simulate,Start Simulate,启动仿真

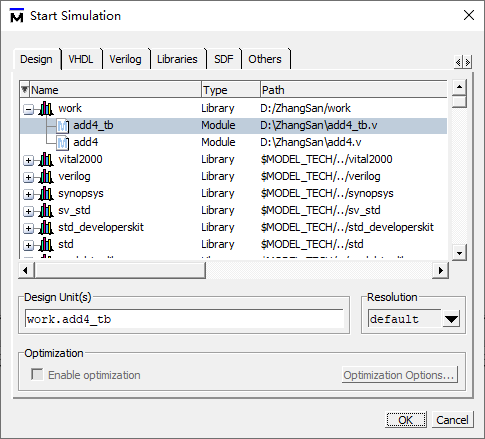

13、选择add4_tb作为顶层,OK

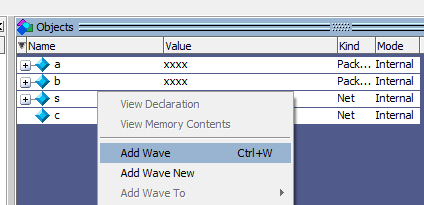

14、全选信号,右击,添加观察信号

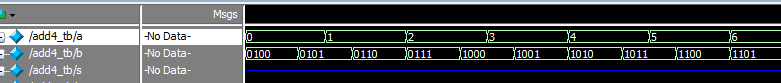

15、点击单步仿真

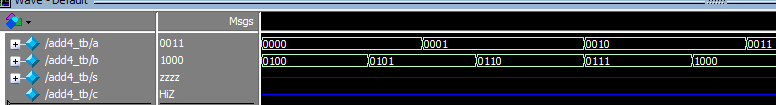

16、观察波形

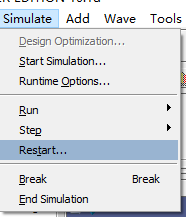

17、如果重新修改了代码,则需要重新编译,然后再点击Simulate->Restart即可。

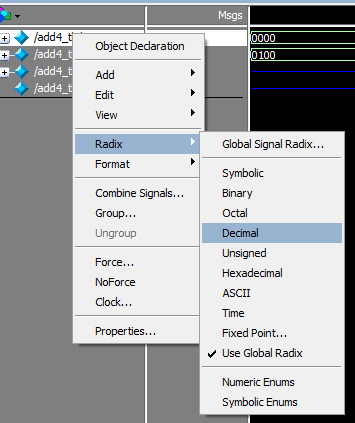

18、也可以其他进制观察信号,如修改为十进制

19、修改后的信号如下