时序逻辑电路应用举例

抢答器

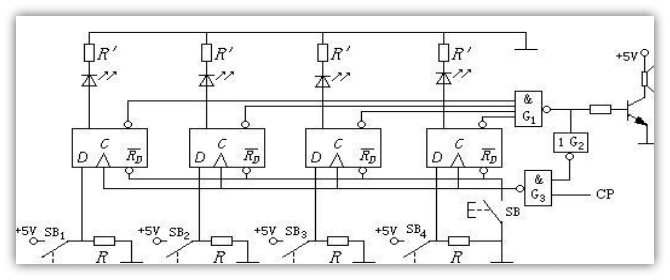

在智力竞赛中,参赛者通过抢先按动按钮,取得答题权。图1是由4个D触发器和2个“与非”门、1个“非”门等组成的4人抢答电路。抢答前,主持人按下复位按钮SB,4个D触发器全部清0,4个发光二极管均不亮,“与非”门G1输出为0,三极管截止,扬声器不发声。同时,G2输出为1, 时钟信号CP经G3送入触发器的时钟控制端。此时,抢答按钮SB1~SB4未被按下,均为低电平,4个D触发器输入的全是0,保持0状态不变。时钟信号CP可用555定时器组成多谐振荡器的输出。

当抢答按钮SB1~SB4中有一个被按下时,相应的D触发器输出为1,相应的发光二极管亮,同时,G1输出为1,使扬声器响,表示抢答成功,另外G1输出经G2反相后,关闭G3,封锁时钟信号CP,此时,各触发器的时钟控制端均为1,如果再有按钮被按下,就不起作用了,触发器的状态也不会改变。 抢答完毕,复位清零,准备下次抢答。

八路彩灯控制器

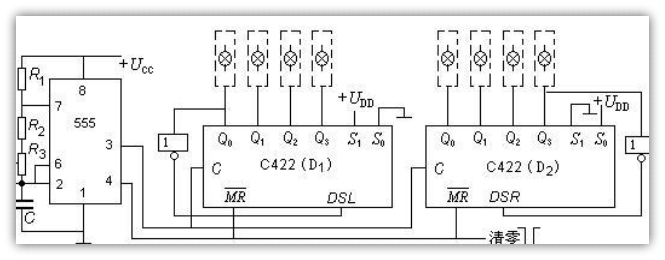

八路彩灯控制器由编码器、驱动器和显示器(彩灯)组成,编码器根据彩灯显示的花型按节拍送出八位状态编码信号,通过驱动器使彩灯点亮、熄灭。给出的八路彩灯控制器电路图中,编码器用两片双向移位寄存器74LS194实现,接成自启动脉冲分配器(扭环形计数器),其中D1为左移方式,D2为右移方式。驱动器电路,当寄存器输出Q为高电平时,三极管T导通,继电器K通电,其动合触点闭合,彩灯亮;当Q为低电平时,三极管截止,继电器复位,彩灯灭。

工作时,先用负脉冲清零,使寄存器输出全部为0,然后在节拍脉冲(可由555定时器构成的多谐振荡器输出)的控制下,寄存器的各个输出Q按下表所示的状态变化,每8个节拍重复一次。这里假定8路彩灯的花型是:由中间向两边对称地逐次点亮,全亮后,再由中间向两边逐次熄灭。