超大规模集成电路 IT产业风云

事件介绍

1970年,美国IBM公司将采用大规模集成电路的大型计算机370系列投放市场。这一举动使日本计算机界顿时气氛异常紧张。

FS(未来系统)作为370系列的下一代产品,将以划时代的设计思想为指导,采用超大规模集成电路芯片制作而成。该产品计划于70年代后半期实现商品化。提起IBM,不愧为当时世界计算机领域的巨人,它占有全球计算机市场份额的70%。日本国内的计算机厂家决不是IBM的对手。

对日本的影响

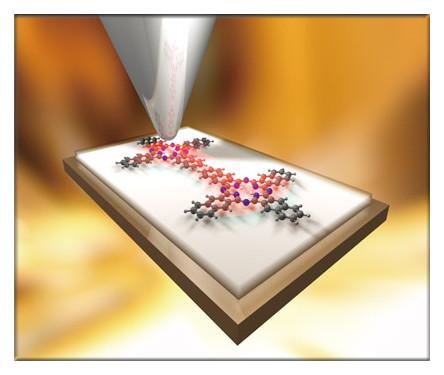

FS一旦出台,日本厂家必将受到难以承受的 打击。为了领先开发出下一代大型计算机用的超大规模集成电路,1976年3月世界上罕见的官民一体化研发机构——超大规模集成电路技术研究组合诞生了。

打击。为了领先开发出下一代大型计算机用的超大规模集成电路,1976年3月世界上罕见的官民一体化研发机构——超大规模集成电路技术研究组合诞生了。

该组合由日本通产省和五大半导体计算机企业组成。该项目的开发,需投入3000亿日元的巨资。业界试图得到1500亿的政府资助,但未能如愿。尽管已故的桥木登美三郎这位自民党信息产业议员联盟会长做了多方努力,仍未能改变政府的决定,最后政府的实际投资仅有300亿日元。国家资助如此之少,使来自各企业的研究人员产生了不满情绪。同时,一种背水一战的悲壮感也油然而生。

富士通公司的福安美一直率地说:“当时,大家都有一种被公司遗弃的感觉,而且并未料到竟然研制出向IBM挑战的产品。”研究组合中这些临时拼凑的人马,开始时各行其道,重要事情只与本公司同来的人交谈。大规模集成电路计算机。甚至出现了在其它公司研究室和本公司研究室之间设置路障的现象。这种互不沟通、互相戒备的局面,使当时的开发气氛十分紧张。

前进的道路并不平坦,正当日本半导体产业犹如日中天之时,PC市场的疾速扩大使需求结构发生了重大变化。1993年,美国依靠微处理器优势,再一次逆转了世界市场的份额。日本方面由于一味地追求微细加工技术,招致了设备投资过大、资本回收恶化的后果。也正是在这一时期,韩国、台湾等发展中国家和地区也开足了马力,进军半导体领域。被誉为"半导体之神"的东芝现常务顾问川西刚指出,为了确保21世纪世界市场的主导权必须采取革命性措施提高生产率,解决投入与回收之间存在的问题。

发展方向

20世纪90年代,电脑向“智能”方向发展,制造出与人脑相似的电脑,可以进行思维、学习、记忆、网络通信等工作。 进入21世纪,电脑更是笔记本化、微型化和专业化,每秒运算速度超过100万次,不但操作简易、价格便宜,而且可以代替人们的部分脑力劳动,甚至在某些方面扩展了人的智能。于是,今天的微型电子计算机就被形象地称做电脑了。