6.1.1 总线的基本概念

一个单处理器系统中的总线分为三类:

(1)CPU内部连接各寄存器及运算部件之间的总线,称为内部总线。

(2)CPU同计算机系统的其他高速功能部件,如存储器、通道等互相连接的总线,称为系统总线。

(3)中、低速I/O设备之间互相连接的总线,称为I/O总线。

1.总线的特性

物理特性 功能特性 电气特性 时间特性

2.总线的标准化

相同的指令系统,相同的功能,不同厂家生产的各功能部件在实现方法上几乎没有相同的,但各厂家生产的相同功能部件却可以互换使用。

【例6.1】(1)某总线在一个总线周期中并行传送4个字节的数据,假设一个总线周期等于一个总线时钟周期,总线时钟频率为33MHz,总线带宽是多少?(2)如果一个总线周期中并行传送64位数据,总线时钟频率升为66MHz,总线带宽是多少?

解:(1)设总线带宽用Dr表示,总线时钟周期用T=1/f表示,一个总线周期传送的数据量用D表示,根据定义可得:

Dr=D/T=D1/T=D×f=4B×33×106=132MB/S

(2)64位=8B

Dr=D/T=D×1/T=D×f=8B×66×106=528MB/S

6.1.2 总线的分类

1.片内总线

片内总线是指芯片内部的总线,如在CPU芯片内部,寄存器与寄存器之间、寄存器与算逻单元ALU之间都由片内总线连接。

2.系统总线

系统总线是指CPU、主存、I/O设备(通过I/O接口)各大部件之间的信息传输线。由于这些部件通常都安放在主板或各个插件板(插卡)上,故又称板级总线(在一块电路板上各芯片间的连线)或板间总线。

按系统总线传输信息的不同,又可分为三类:数据总线、地址总线和控制总线。

3.通信总线

这类总线用于计算机系统之间或计算机系统与其他系统(如控制仪表、移动通信等)之间的通信。

6.1.3总线的结构

根据连接方式不同,单机系统中采用的总线结构有两种基本类型:①单总线结构:②多总线结构。

1.单总线结构

在许多单处理器的计算机中,使用单一的系统总线来连接CPU、主存和I/O设备,叫做单总线结构。

单总线结构中,要求连接到总线上的逻辑部件必须高速运行,以便在某些设备需要使用总线时,能迅速获得总线控制权;而当不再使用总线时,能迅速放弃总线控制权。单总线结构容易扩展成多CPU系统。

2.多总线结构

单总线系统中,由于所有的高速设备和低速设备都挂在同一个总线上,且总线只能分时工作,即某一时间只能允许一对设备之间传送数据,这就使信息传送的效率和吞吐量受到极大限制。为此出现了图6.2所示的多总线系统结构。

6.1.4 总线的内部结构

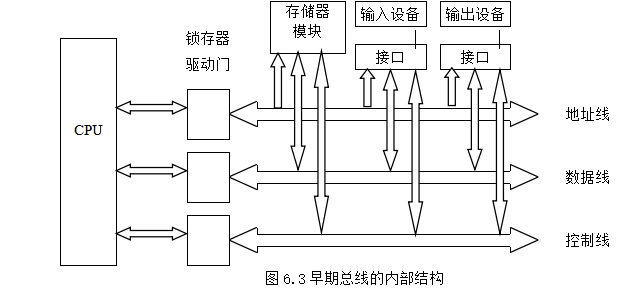

早期总线的内部结构如图6.3所示。它实际上是处理器芯片引脚的延伸,是处理器与I/0设备适配器的通道。

这些线按其功能可分为三类:地址线、数据线和控制线。地址线是单向的,用来传送主存与设备的地址;数据线是双向的,用来传送数据;控制线对每一根线来讲是单向的(CPU发向接口,或接口发向CPU),用来指明数据传送的方向(存储器读、存储器写、I/0读、I/O写),中断控制(请求、识别)和定时控制等。

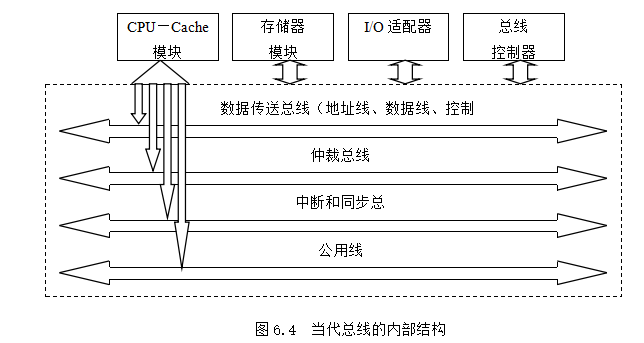

图6.4示出了当代流行的总线内部结构,它是一些标准总线,追求与结构、CPU、技术无关的开发标准,并满足包括多个CPU在内的主控者的环境要求。

l 数据传送总线:由地址线、数据线、控制线组成。其结构与图6.3中的简单总线相似,但一般是32条地址线,32或64条数据线。为了减少布线,64位数据的低32位数据线常常和地址线采用多路复用方式。

l 数据传送总线:由地址线、数据线、控制线组成。其结构与图6.3中的简单总线相似,但一般是32条地址线,32或64条数据线。为了减少布线,64位数据的低32位数据线常常和地址线采用多路复用方式。

l 仲裁总线:包括总线请求线和总线授权线。

l 中断和同步总线:用于处理带优先级的中断操作,包括中断请求线和中断认可线。

公用线:包括时钟信号线、电源线、地线、系统复位线以及加电或断电的时序信号线等。